Cadence Allegro PCB设计全流程实战教程(视频+图文,零基础可学)

【课程核心优势】

【适配人群】

【学习收获】

第一部分:Allegro基础环境与工程准备

[xx_insert_post station_article=”3447″]

暂无菜单项

[xx_insert_post station_article=”3447″]

登录后参与聊天

成为一名合格的PCB设计工程师?不想再做基础打杂,真正掌握可直接上岗的PCB设计核心技能? 智行者IC社区2026年4月PCB设计工程师专项课程,4月9日正式开课!专门针对零基础小白、转行从业者,以及想进阶提升的在岗人员,全程实战教学,手把

想转行做硬件工程师?或者想提升 PCB 设计技能? 智行者 IC 社区 2026 年 4 月 PCB + 嵌入式硬件专项实训,4 月 9 日正式开课! 针对目前行业 “重理论、轻实操” 的就业痛点,本次实训不搞题海战术,全程落地企业在岗标准

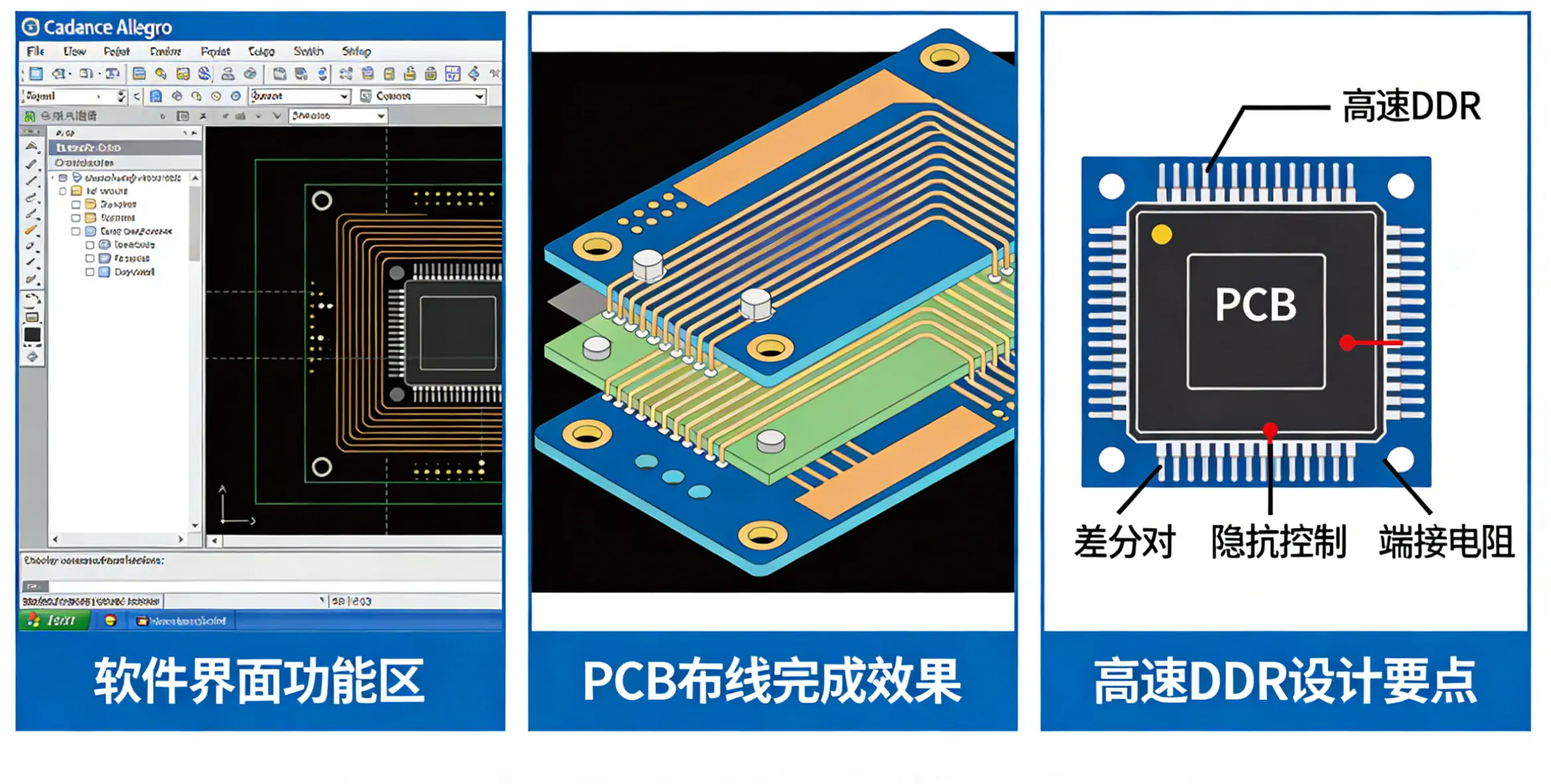

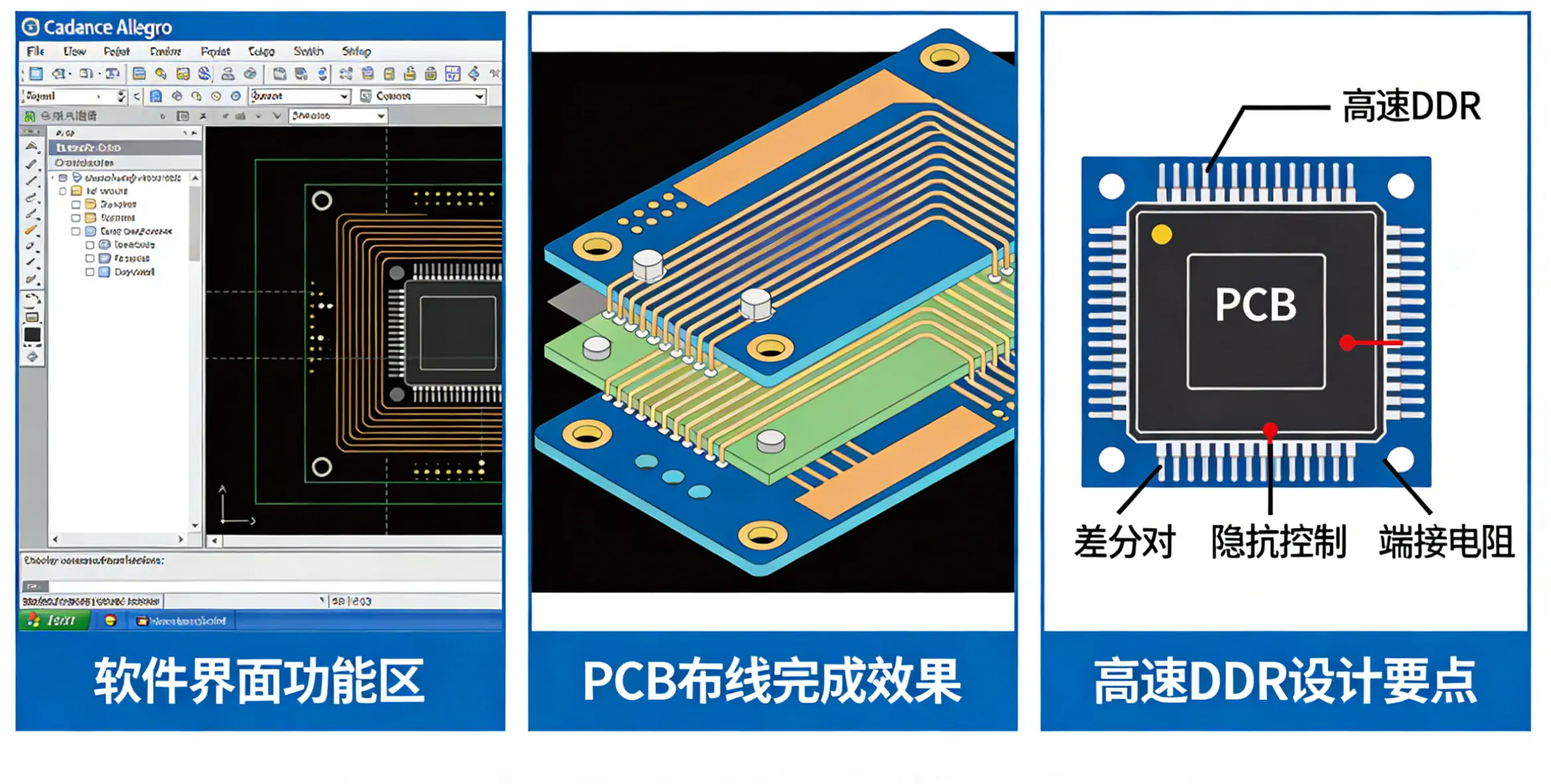

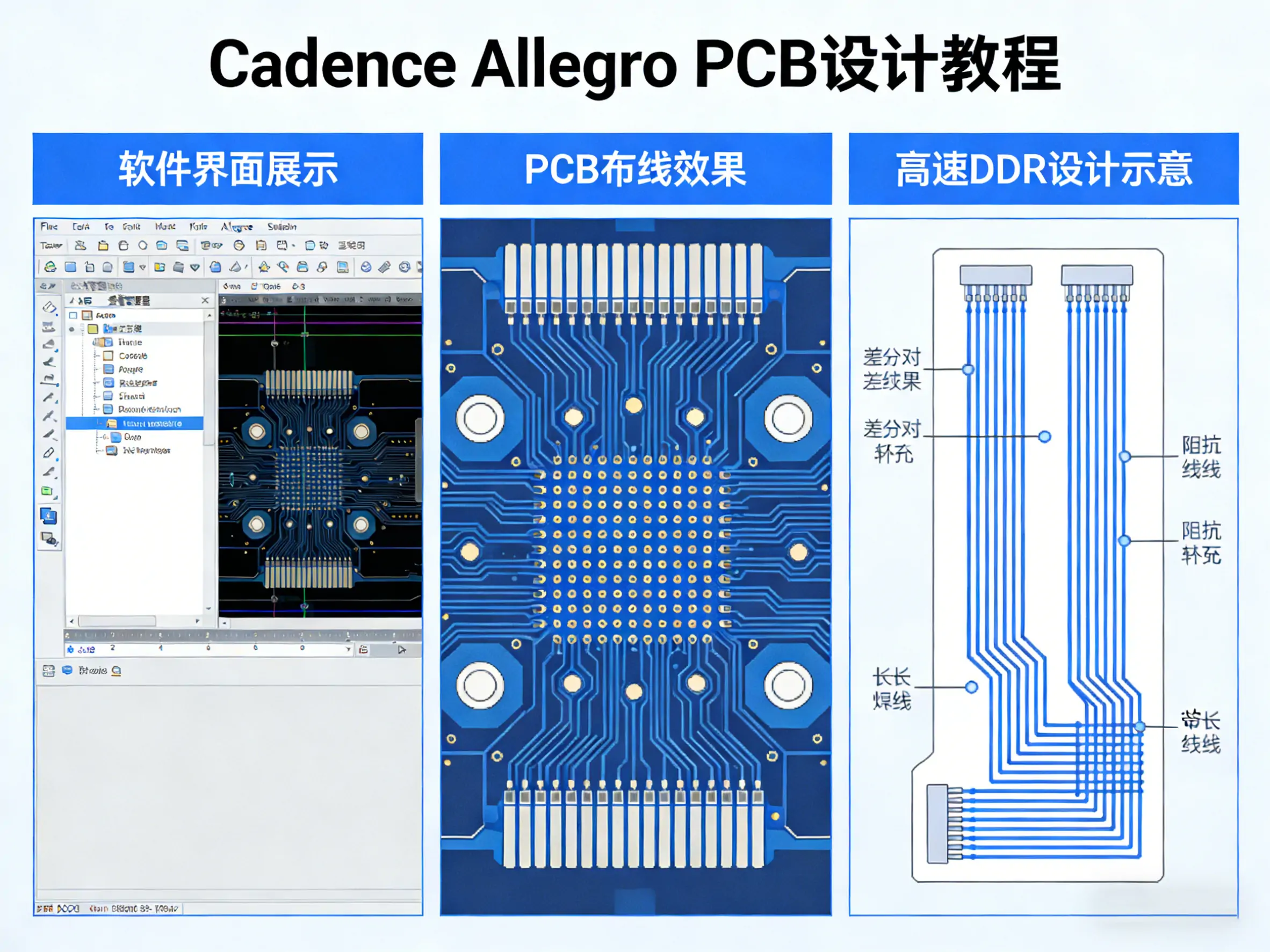

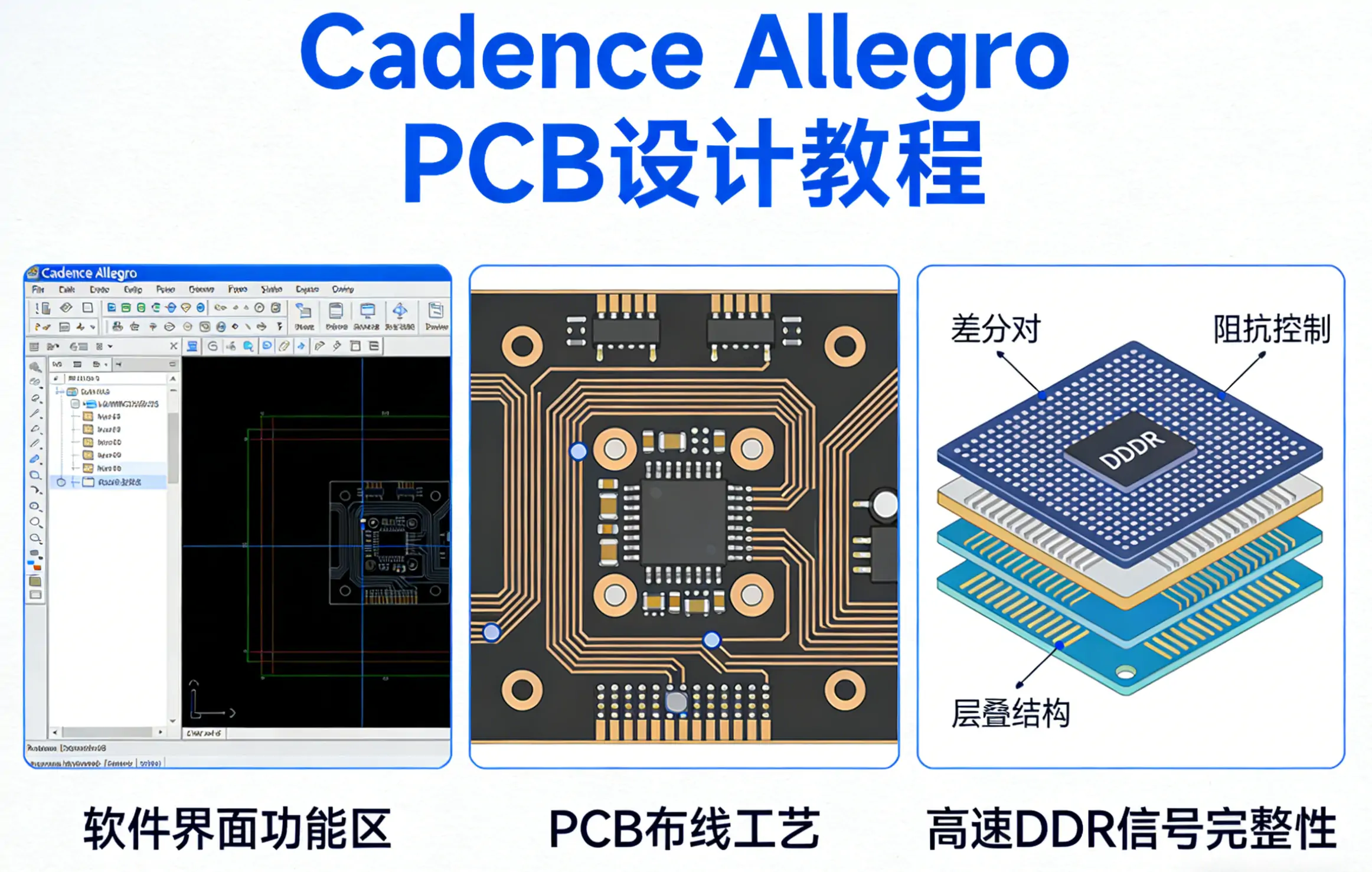

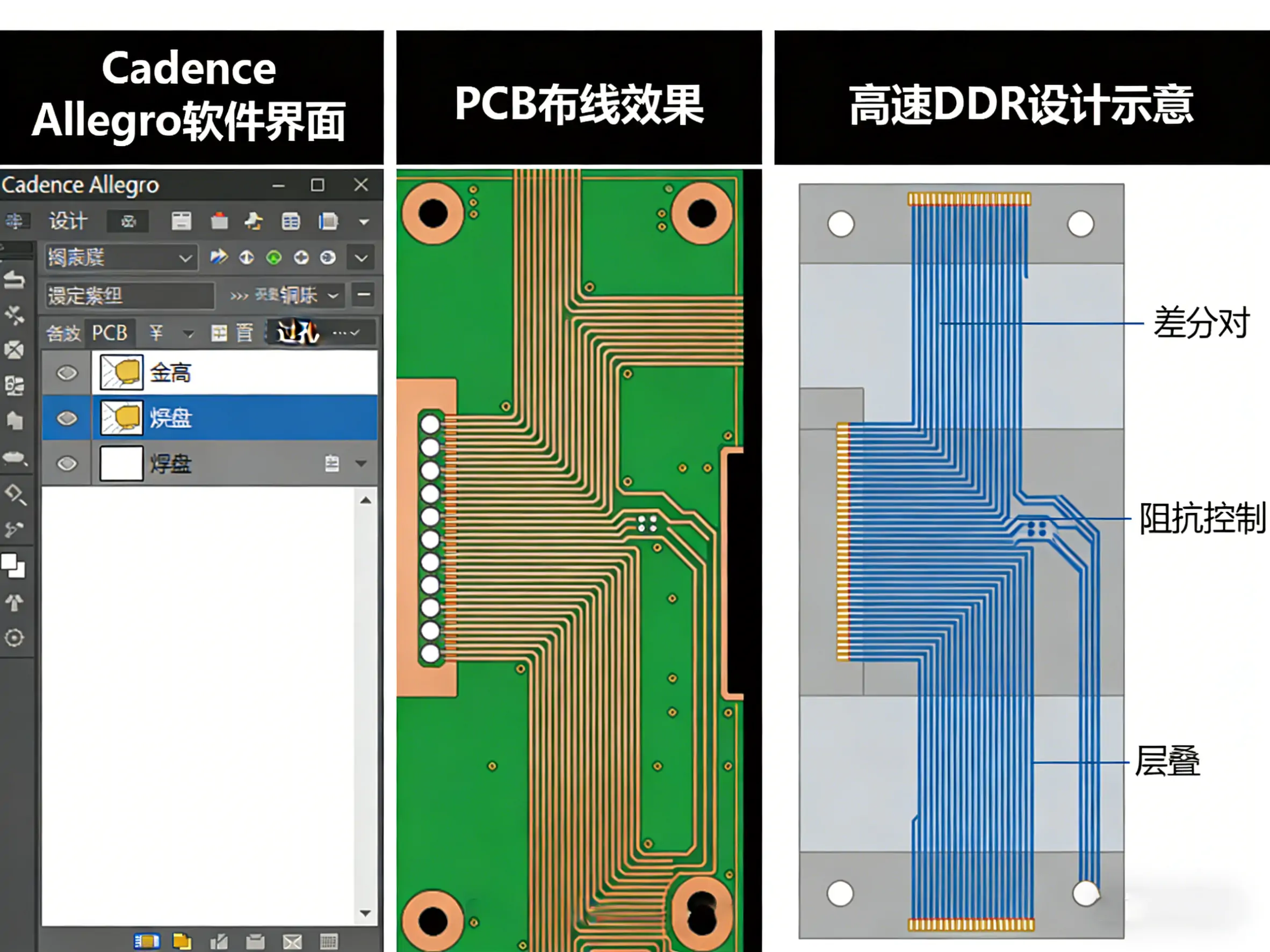

Cadence Allegro PCB设计全流程实战教程(视频+图文,零基础可学) 大家好,这里是智行者IC社区,专注PCB设计与硬件开发实战。今天给大家带来一套完整的Cadence Allegro PCB设计全流程实战教程,从Allegr

对标企业量产标准 精通 Allegro 全流程实战 在硬件研发领域,PCB设计与嵌入式开发是核心技能,而熟练运用工业级设计工具Cadence Allegro,更是成为资深硬件工程师的必备条件。为帮助更多从业者、应届生及爱好者突破技能瓶颈,快

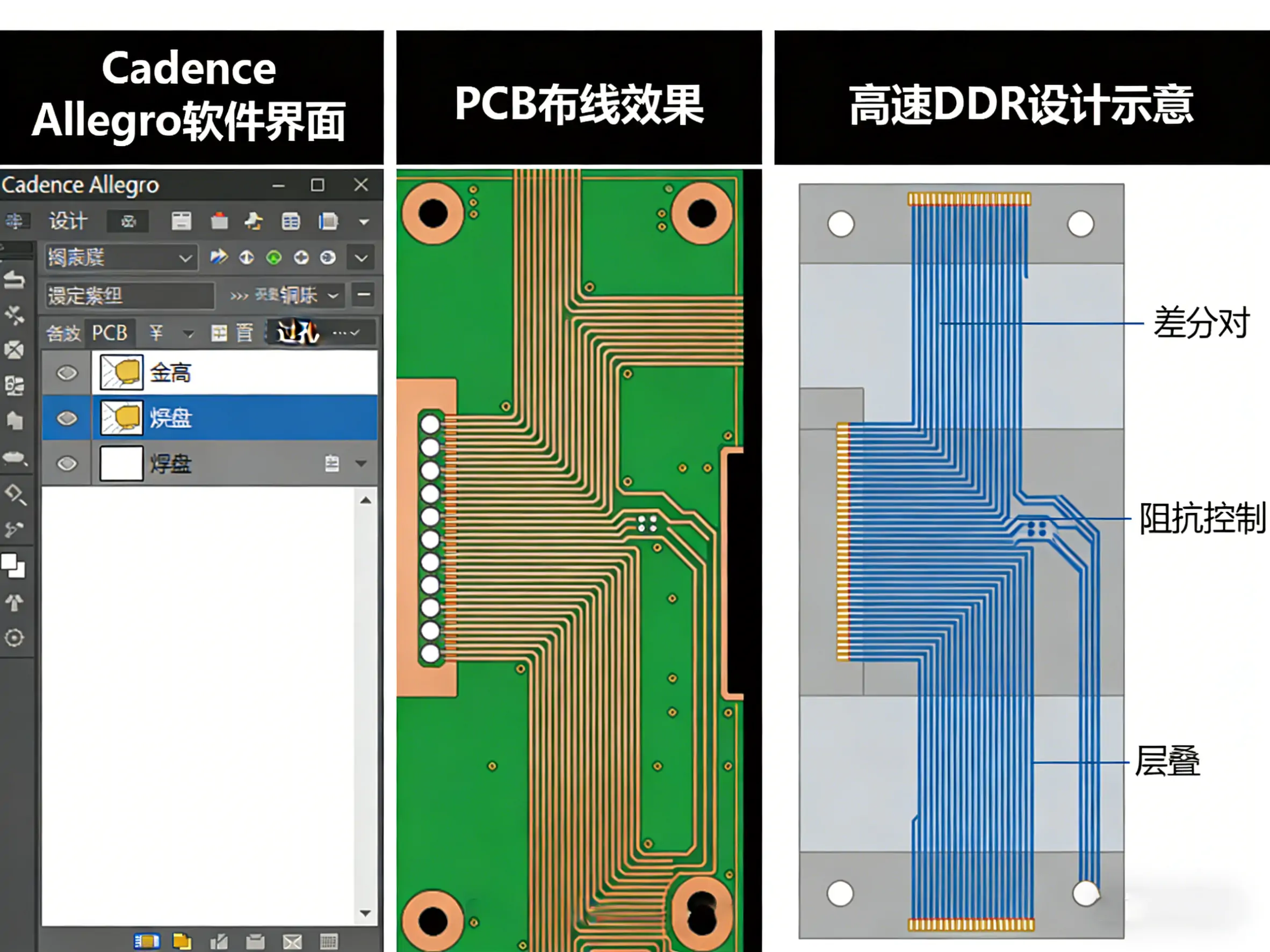

开课日期:2026 年 1 月 20 日 适合人群:有基础硬件设计经验的工程师、电子技术从业者、希望进阶高速 PCB 设计的技术人员 学习形式:线下实训 + 线上答疑 + 项目复盘 🎯 为什么选择这门课? 在高速硬件开发领域,Cadence

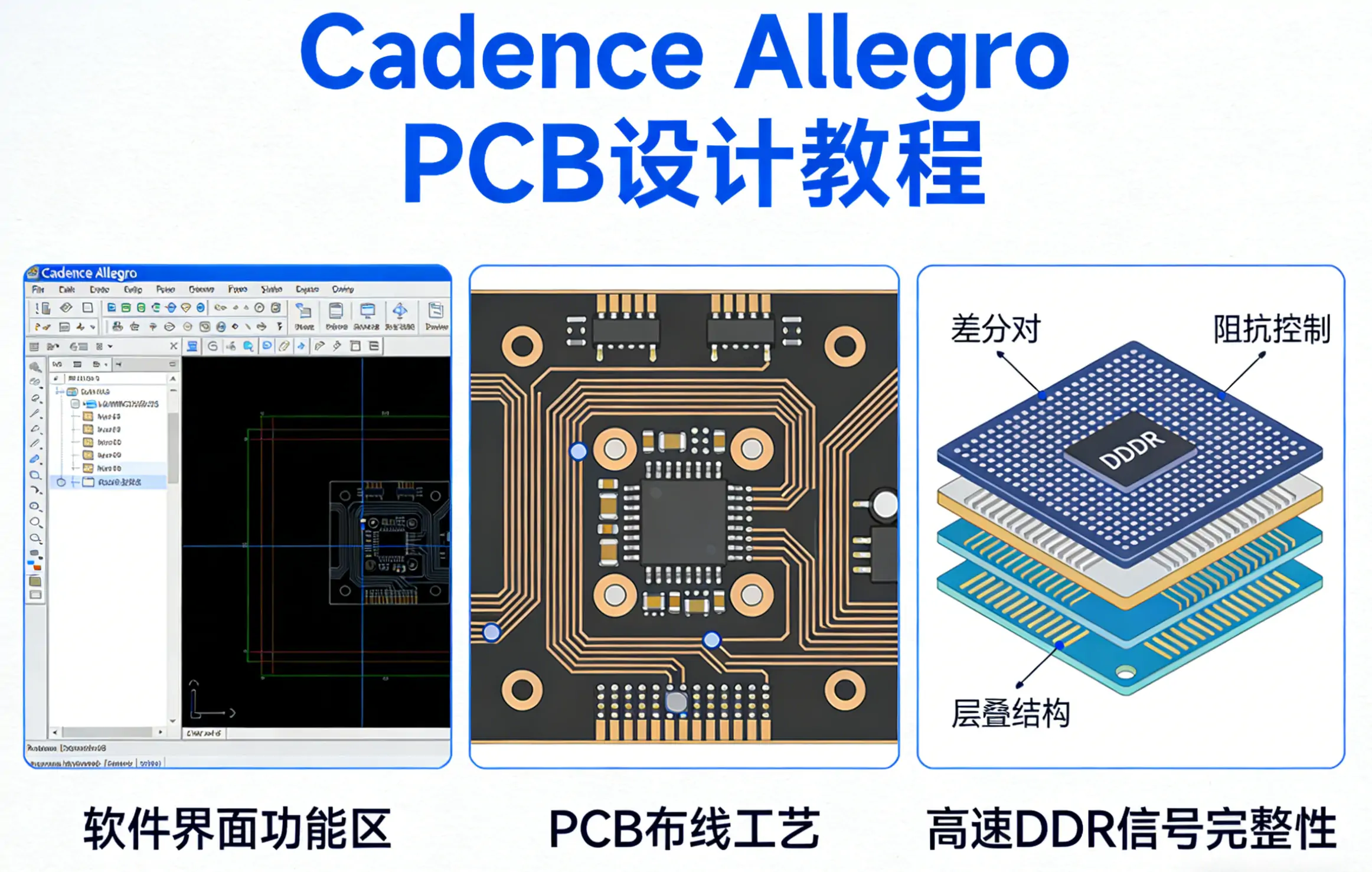

🔥 2026.01.06 重磅开营 | 全真实项目驱动 | Cadence Allegro16.6 全程实操 🔥 ✅ 核心亮点 工具实战:Cadence Allegro16.6 全流程教学,从原理图导入到 PCB Layout、DRC 检查

PCB+嵌入式硬件全项目案例实战 学硬技能 拿高薪就来智行者IC社区! 如果你想从“只会画简单电路”进阶到“能独立完成商用硬件项目”,或是想突破“懂理论但不会落地”的瓶颈——这门《PCB+嵌入式硬件全项目案例实战》就是为你量身打造的实战课!

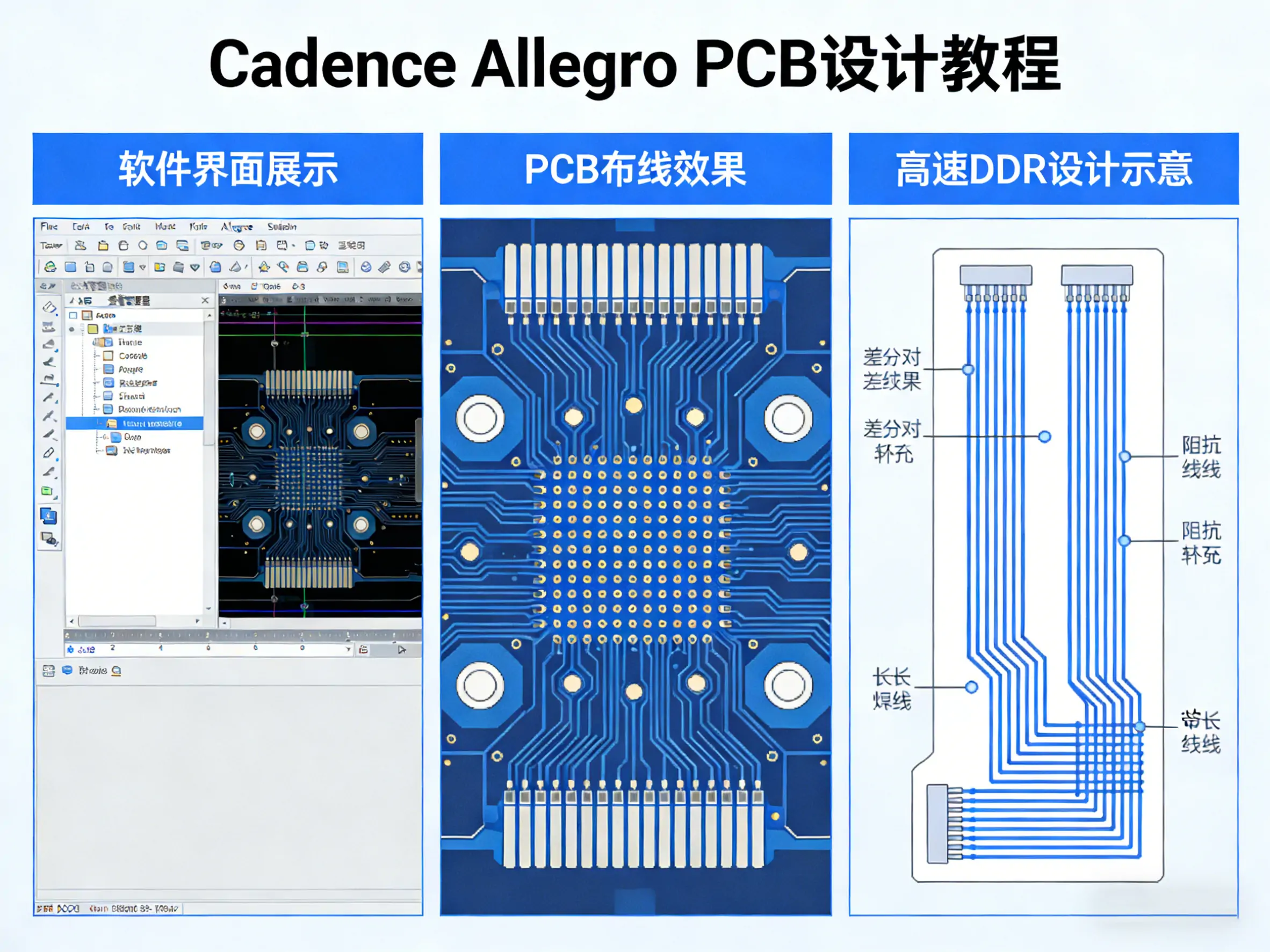

基于Cadence Allegro的PCB实战课程 2025年11月最新Cadence Allegro 16.6 PCB+嵌入式硬件实战课程,从零基础到中高端项目全流程!涵盖DDR4/PCIe高速信号、BGA封装、EMC设计,学完胜任通信/

一、课程大纲(总课时:60 课时,小班制 15 人以内) 模块 1:入门筑基阶段(10 课时) 模块 2:核心技能进阶阶段(25 课时) 模块 3:真实项目实战阶段(15 课时) 模块 4:就业赋能阶段(10 课时) 二、课程描述 本课程是

一、课程大纲(总课时:60 课时,小班制 15 人以内) 模块 1:入门筑基阶段(10 课时) 模块 2:核心技能进阶阶段(25 课时) 模块 3:真实项目实战阶段(15 课时) 模块 4:就业赋能阶段(10 课时) 二、课程描述 本课程是